本研究は半導体理工学研究センターにおける「大学との共同研究」の研究テーマとして、平成16年度より開始したものです。

本研究は半導体理工学研究センターにおける「大学との共同研究」の研究テーマとして、平成16年度より開始したものです。

集積回路技術の進歩による素子の高速化と搭載トランジスタ数増大によりプロセッサの性能は指数的に向上してきたが、増大する消費電力は性能向上を妨げる大きな問題であり、また、最小加工寸法の微細化による配線遅延増大のため、VLSI全体にクロックを伝播させる従来の同期式設計は、クロックスキューの問題からもクロック消費電力の問題からも効率が悪い。本研究の目的は、従来の設計手法が本質的に抱える上記の問題を解決し、高性能かつ電力消費の小さいプロセッサの実現手法を提示することである。

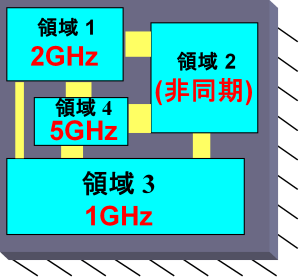

図1: GALSの構成

そこで、VLSI構成方式としてGALS (Globally Asynchronous LocallySynchronous) 型構成(図1を参照)を採用し、VLSI内部において動的電圧制御(DVS: Dynamic Voltage Scaling) を空間的にも時間的にも細粒度で行うことにより低消費電力化をはかることを提案する。本研究の目的は提案手法により、高性能かつ低電力消費プロセッサの実現可能性を提示することであり、具体的な目標は以下の2点である。

(目標1)ハイエンドプロセッサに上記手法を適用した場合の有効性を実証すること

この実現のために、高品質な非同期インタフェースの開発、GALS-DVSが有効なマイクロアーキテクチャの提案、さらに、細粒度な動的電圧制御方式の提案を行う。

(目標2)提案手法を用いたVLSIシステムの設計技術を確立すること。

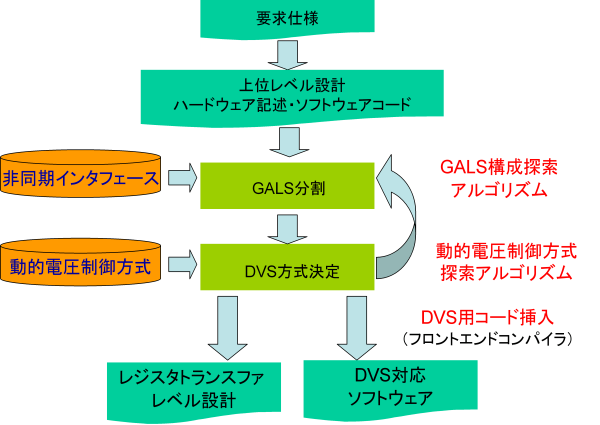

この実現のために、具体的には図2に示す設計フローの確立を目指す。

図2: 設計フロー